- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-FIR (Altera)IP FIR COMPILER

�� �

�

�

�1–2�

�Chapter� 1:� About� the� FIR� Compiler�

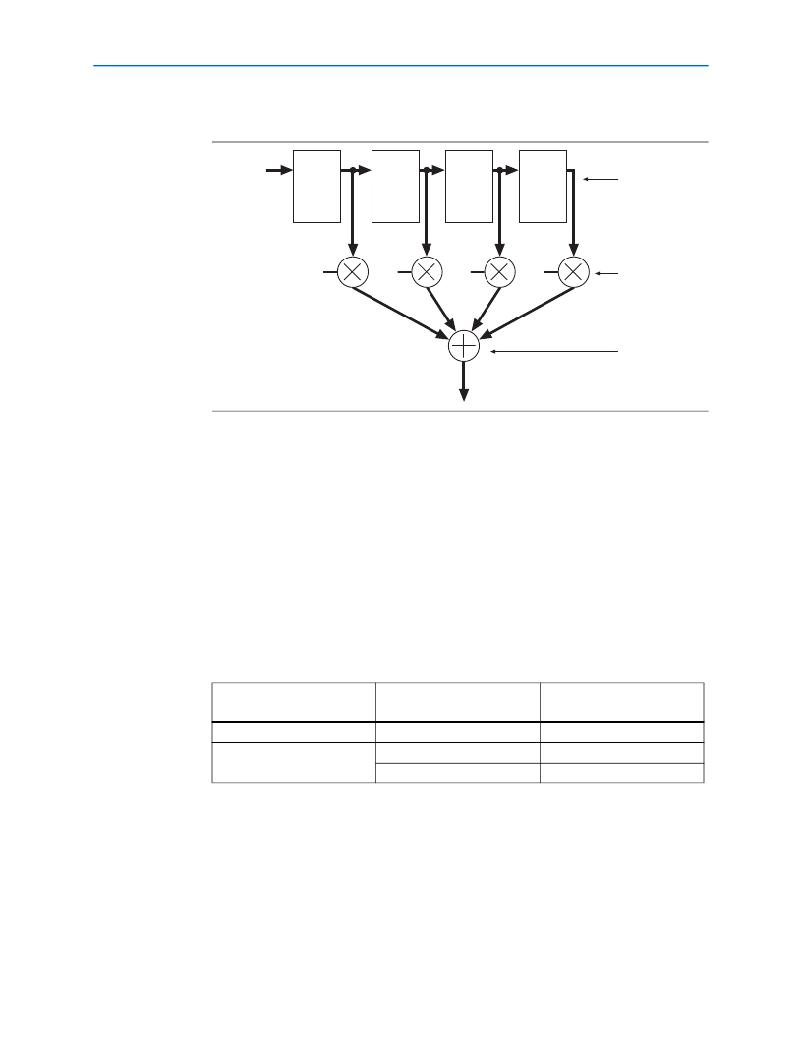

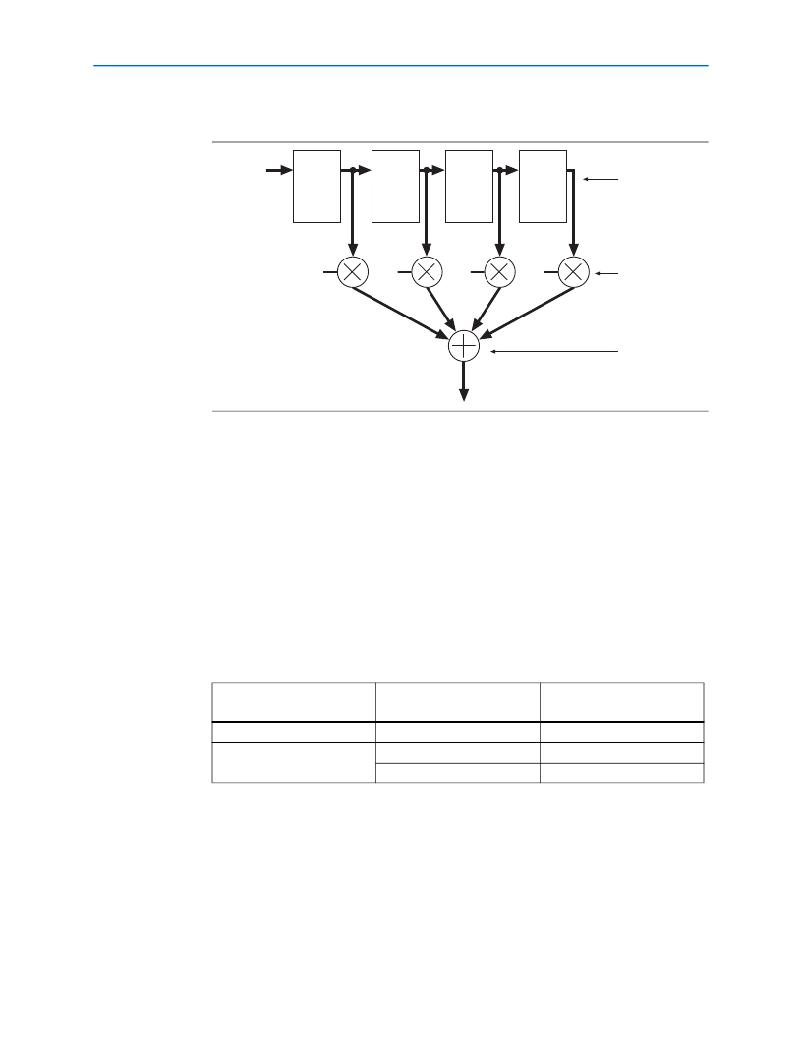

�The� structure� of� a� FIR� filter� is� a� weighted,� tapped� delay� line� as� shown� in� Figure� 1–2� .�

�Figure� 1–2.� Basic� FIR� Filter�

�xin�

�Z� -1�

�C� 0�

�Z� -1�

�C� 1�

�Z� -1�

�C� 2�

�Z� -1�

�C� 3�

�Tapped�

�Delay� Line�

�Coefficient�

�Multipliers�

�Adder� Tree�

�yout�

�The� filter� design� process� involves� identifying� coefficients� that� match� the� frequency�

�response� specified� for� the� system.� These� coefficients� determine� the� response� of� the�

�filter.� You� can� change� the� signal� frequencies� that� pass� through� the� filter� by� changing�

�the� coefficient� values� or� adding� more� coefficients.�

�DSP� processors� have� a� limited� number� of� multiply� accumulators� (MACs),� and� require�

�many� clock� cycles� to� compute� each� output� value� (the� number� of� cycles� is� directly�

�related� to� the� order� of� the� filter).�

�A� dedicated� hardware� solution� can� achieve� one� output� per� clock� cycle.� A� fully�

�parallel,� pipelined� FIR� filter� implemented� in� an� FPGA� can� operate� at� very� high� data�

�rates,� making� FPGAs� ideal� for� high-speed� filtering� applications.�

��a� 120-tap� FIR� filter� with� a� 12-bit� data� input� bus.�

��Clock� Cycles� to�

�Device�

�DSP� processor�

�FPGA�

�Implementation�

�1� MAC�

�1� serial� filter�

�1� parallel� filter�

�120�

�12�

�1�

�Compute� Result�

��(1)� If� you� use� the� FIR� Compiler� to� create� a� filter,� you� can� also� implement� a� variable� filter� in� a� FPGA� that� uses� from� 1�

�to� 120� MACs,� and� 120� to� 1� clock� cycles.�

�The� Altera� FIR� Compiler� speeds� the� design� cycle� by:�

��■�

�■�

�Generating� the� coefficients� needed� to� design� custom� FIR� filters.�

�Generating� bit-accurate� and� clock-cycle-accurate� FIR� filter� models� (also� known� as�

�bit-true� models)� in� the� Verilog� HDL� and� VHDL� languages� and� in� the� MATLAB�

�environment.�

�?� May� 2011� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-NCO

IP NCO COMPILER

IP-NIOS

IP NIOS II MEGACORE

IP-PCI/MT64

IP PCI 64BIT MASTER/TARGET

IP-PCIE/8

IP PCI EXPRESS, X8

IP-POSPHY4

IP POS-PHY L4

IP-RIOPHY

IP RAPID I/O

IP-RLDRAMII

IP RLDRAM II CONTROLLER

IP-RSDEC

IP REED-SOLOMON DECODER

相关代理商/技术参数

IP-FIRII

功能描述:开发软件 FIR Compiler II MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPFLBPT2

制造商:Carlo Gavazzi 功能描述:IL 35MM MUSH P-P PL 22MM RED

IPG1-0-90

制造商:Sensata Technologies 功能描述:1 Pole

IPG1-1-41-203-90

制造商:Sensata Technologies 功能描述:1 Pole

IPG1-1-51-103-A-00-V

制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic 1Pole 10A 65VDC

IPG1-1-52-303-A-00-V

制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic 1Pole 30A 65VDC

IPG1-1-61-153-00-V

制造商:Airpax 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A 制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A

IPG1-1-61-153-90-V

制造商:Airpax 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A 制造商:Sensata Technologies 功能描述:Circuit Breaker Magnetic Circuit Protectors 1Pole 15A